### Study of 10GBase-T Transmitter

指導教授:汪重光

學生:葉治億

- Survy on IEEE 802.3an task force material

- The impairment of the DAC

- Random walk method

- Dynamic random walk

- Working Items

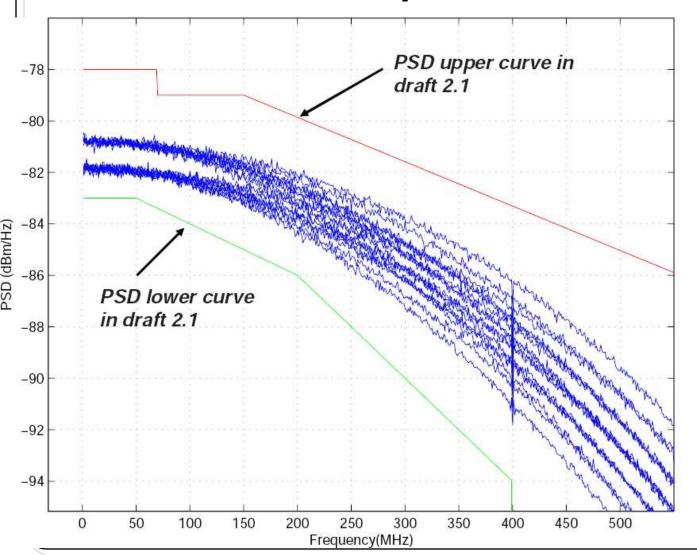

### PSD Specification

#### Note:

- With 2V +/- 6% at the transformer output, the lower PSD curve has smaller margin at lower end.

- 2V +/- 6% with the filter tolerances as specified meets the power spec

- Upper PSD has a larger margin, especially the lower 0-70MHz range.

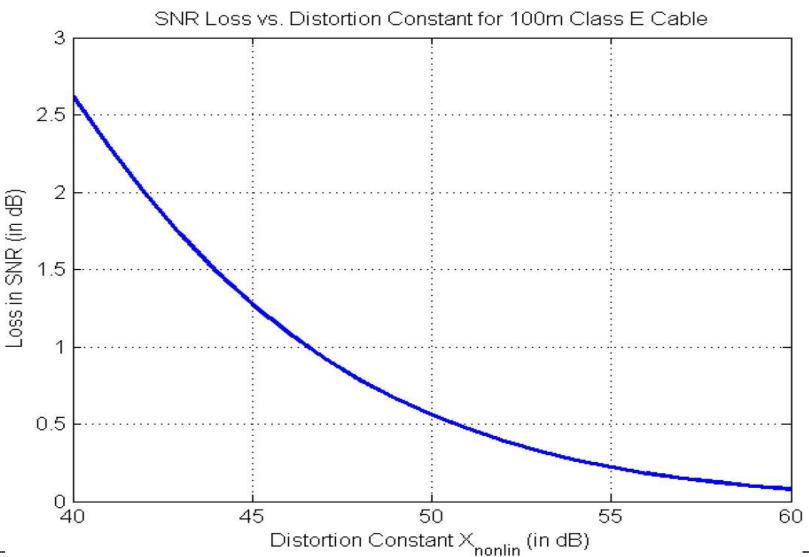

### Nonlinear Distortion

### National Taiwan University

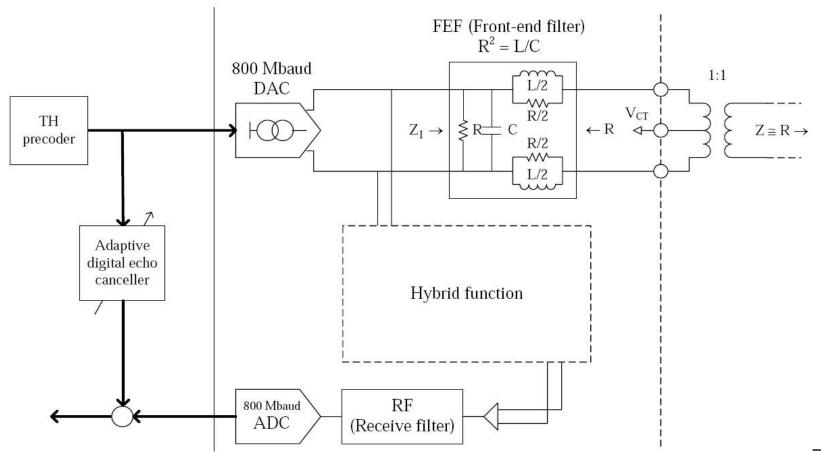

# Transmitter from Broadcom (I)

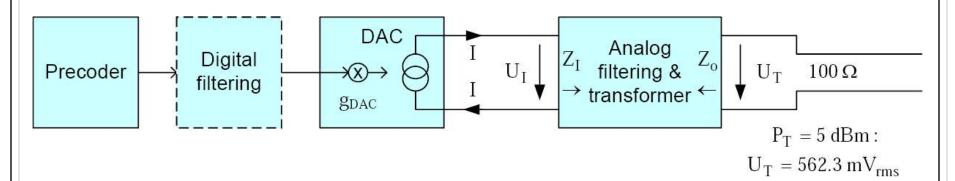

No digital filtering, T-spaced DAC, front-end filter with frequency-dependent input impedance Z<sub>I</sub> and constant output impedance R

[Gottfried Ungerboeck and Scott Powell, "10GBASE-T Cable characteristics, from end solutions and preceders", IEEE P802.3an Task Force, Atlanta, March 22-24, 2005]

**National Taiwan University**

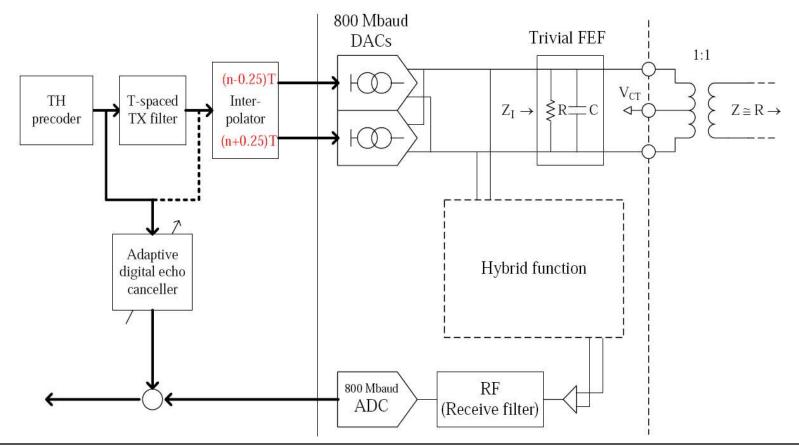

# Transmitter from Broadcom (II)

Digital TX-filtering & T/2-interpolation, T/2-overlapping DACs, trivial front-end filter

### National Taiwan University

## Transmitter from Broadcom (III)

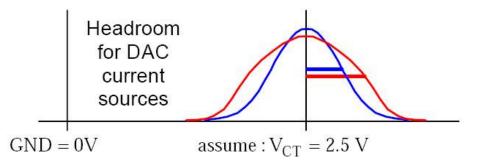

$Baseline \ approach: \quad I = 15.9 \ mA_{rms}, \ \ U_I = 891.1 \ mV_{rms,diff} \quad \stackrel{\Delta}{=} \quad V_{CT} \pm 445 \ mV_{rms}$

$Preferred \, appraoch: \ \, I=12.7 \, mA_{rms}, \, U_{I}=630.7 \, mV_{rms,diff} \quad \stackrel{\Delta}{=} \quad V_{CT} \pm 315.3 mV_{rms}$

Preferred approach has lower (-3 dB) rms-voltage at DAC outputs than baseline approach, but (presumably) higher peak-to-average ratio.

### The Impairment of the DAC

- DC accuracy

- Random errors: device mismatches

- Systemic errors:

- Linear gradient: common centroid

- Higher order effects

- AC accuracy

- Voltage Fluctuation

- Control signals feedthrough

- Clock synchronization

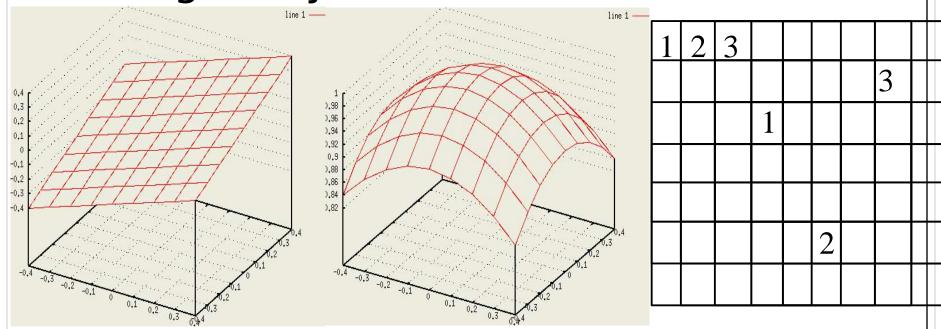

### Random Walk Method

Use random walk method to mitigate systemic mismatch

[Geert A. M. et al, "A 14-bit Intrinsic Accuracy Q<sup>2</sup> Random Walk CMOS DAC", IEEE JSSC Vol. 34, No. 12, Dec. 1999]

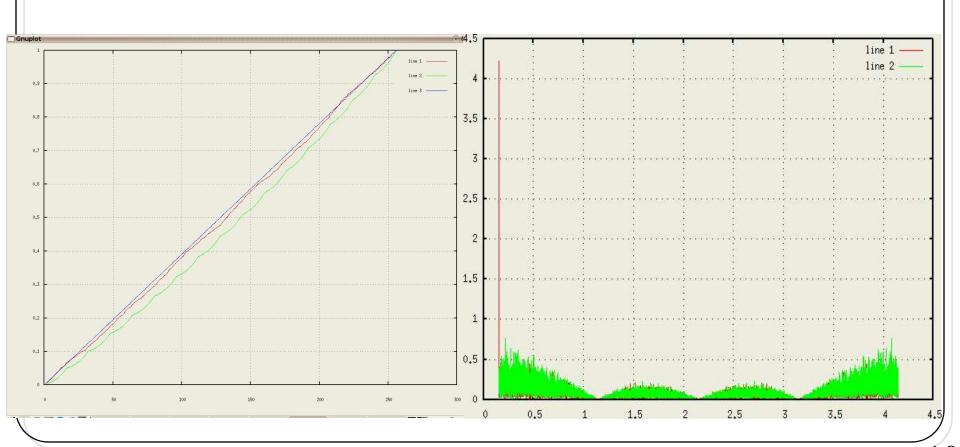

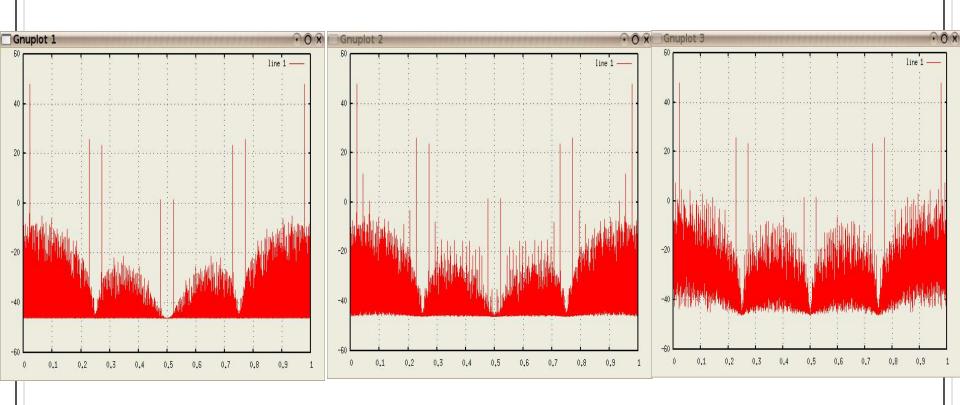

## **Dynamic Random Work**

Use switch as round robin

Spur in the Sine Wave

Simulation

## Working Items

#### **10Gbase-T Transmitter**

☑Transmitter architecture design

☑DAC design

□Circuits design

□Layout and verification

□Line driver design

□System design

□Circuits design

□Layout and verification

□Hybrid design

□System design

□Circuits design

□Layout and verification

■Finished ☑On-going □Future work

September 20, 2005 NTU/NSC Confidential